Avec Quickpath, Intel va refondre ses architectures serveurs

En adoptant un système de bus point à point similaire à celui de l'Hypertransport d'AMD, Intel va permettre une rénovation en profondeur des architectures de serveurs utilisant ses puces. Cette refonte devrait se traduire par des designs plus simples mais aussi plus performants. Elle aura un impact significatif sur les serveurs d'entrée de gamme à base de puces Xeon mais aussi sur les systèmes haut de gamme et notamment sur la nouvelle génération de grands serveurs Itanium.

Si l'on parle aujourd'hui beaucoup de l'architecture Nehalem, qui fera son apparition à la fin de l'année dans les serveurs bi-processeurs et sur les PC de bureau, c'est avant tout du fait de l'adoption par Intel d'une architecture de bus point à point similaire à celle d'AMD. QuickPath, c'est son nom, promet de révolutionner la conception des serveurs Intel, qu'il s'agisse des serveurs x86 ou, plus important pour certains, des serveurs Itanium.

Le bus d'interconnexion QuickPath (QuickPath Interconnect ou QPI) est un bus point à point qui permet, à l'instar d'Hypertransport dans l'architecture d'AMD, d'interconnecter entre eux les différents composants d'un serveur. Dans sa déclinaison initiale, QuickPath dispose d'un débit bidirectionnel de 25,6 Go/s (2x12,8 Go/s dans chaque direction) sur les puces serveurs Xeon gravées en 45 nm et de 19,2 Go/s (2x8,6 Go/s) sur les puces Itanium "Tukwila". L'adoption de QPI dans les puces Intel s'accompagne également de l'intégration dans chaque puce de contrôleurs mémoires à l'instar de ce qu'a déjà réalisé AMD avec l'Opteron. Les premières puces intégrant le bus QPI devraient être les nouvelles générations de Xeon "Nehalem" attendues en fin d'année ainsi que le prochain Itanium "Tukwila".

Des architectures plus simples, plus économiques et plus performantes

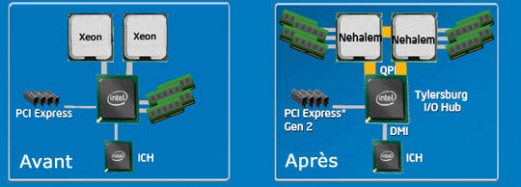

Pour les serveurs bi-processeurs, Quickpath va offrir deux grands avantages. Dans un premier temps, la technologie va permettre de simplifier les architectures des serveurs x86 Intel, comme Hypertransport l'a fait pour AMD. Ensuite QuickPath va doper les performances. Dans une configuration bi-processeur, chaque Xeon "Nehalem" disposera de deux bus QPI soit un total de plus de 50 Go de bande passante pour échanger avec les autres composants du système. Ces échanges se feront de plus avec une bien plus faible latence qu'avec l'ancien bus partagé des Xeon.

Dans la pratique, sur un système bi-processeur, chaque processeur sera relié à l'autre par deux liens QPI et disposera d'un lien vers le contrôleur d'entrées/sorties. L'adoption de QPI devrait donc se traduire par des gains massifs de performances pour toutes les applications faisant un usage intensif de la mémoire mais aussi des entrées/sorties.

Une relance de la bataille AMD/Intel sur les serveurs x86 haut de gamme

Comme dans le cas des Opteron, l'intérêt de QPI devrait encore augmenter avec l'accroissement des liens disponibles sur chaque puce. Ainsi les successeurs des actuels Xeon MP (pour serveurs multi-processeurs), les Xeon "Nehalem EP", disposeront de trois liens QPI, de quoi assembler des systèmes capables d'accueillir jusqu'à 8 processeurs sans recourir à un chipset spécifique (pour mémoire, les actuels Xeon MP ne fonctionnent qu'en configuration quadri-processeur, sauf s'ils sont associés à un chipset spécifique comme celui qu'a développé IBM pour ses puces).

Pour ce segment très spécifique des serveurs x86 de haut de gamme, l'arrivée de QPI devrait donc se traduire par l'émergence de systèmes SMP Intel à 8 sockets offrant un rapport performance/prix inégalé par rapport aux systèmes Intel haut de gamme d'aujourd'hui. Il faudra toutefois attendre la seconde moitié de l'année 2009, et la sortie des Xeon "Nehalem EP", pour voir apparaître ces systèmes. Grâce à Hypertransport, HP et Sun proposent dès aujourd'hui des systèmes Opteron à huit voies, performants et relativement économiques.

Mais l'impact le plus grand de QPI dans les premiers mois de son existence devrait se faire sentir dans un segment stratégique, celui des serveurs de très haut de gamme. QPI va en effet remplacer le vieux bus des puces Itanium et doper sérieusement la bande passante des puces haut de gamme d'Intel. Chaque puce Tukwila sera dotée de quatre bus QPI pleine largeur et de deux bus demi-largeur. Avec un tel équipement, la bande passante entre les processeur devrait être multipliée par neuf, tandis que l'intégration de deux contrôleurs mémoires dans chaque processeur devrait aussi accroître par un facteur de six la bande passante mémoire. De quoi redonner un coup de jeune à une architecture dont les fondements en entrées/sorties n'avaient guère évolués depuis 10 ans.

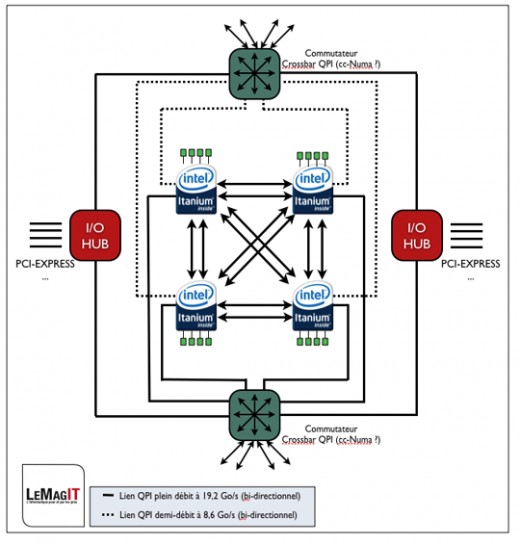

QPI devrait aussi permettre une refonte en profondeurs des architectures des grands systèmes SMP Itanium. Architecturalement, HP pourrait ainsi renouer avec des concepts de design qu'il avait déjà utilisé avant le lancement des premiers Superdome sur ses serveurs V2500. A l'époque, HP avait développé une architecture baptisée Scalable Computing Architecture; en fait une architecture à base de crossbar permettant d'interconnecter plusieurs systèmes entre eux pour les faire apparaître comme un seul grand système cc-Numa (voir à ce propos l'illustration ci-dessous).

Il semble que ce soit ce genre de concept sur lequel travaillent plusieurs constructeurs familiers de l'architecture Itanium, dont Bull et HP. L'idée est en fait de développer un chipset, agissant comme un commutateur QPI et qui serait aussi capable de gérer la cohérence de cache entre les systèmes reliés par le commutateur.

Vers des serveurs Itanium haut de gamme plus modulaires ?

Dans la pratique, un serveur Itanium haut de gamme pourrait ressembler à un agrégat de plusieurs systèmes autonomes, chacun disposant typiquement de 4 processeurs et de deux chipsets cc-Numa, le tout interconnecté par des bus QPI afin d'assurer une redondance optimale. Selon les besoins, chaque cellule de 4 processeurs pourrait être reliée à d'autres pour constituer un système de plus grande taille, ou être totalement séparée afin de constituer une partition autonome. Une telle architecture pourrait être physiquement packagée dans un châssis de serveur lames haut de gamme (ce serait l'idée d'HP pour ses prochains systèmes Itanium), où le fond de panier assure les communications inter-lames et les communications entre lames et cartes d'entrée/sorties.

Notons au passage qu'un tel concept pourrait aussi s'appliquer à l'élaboration de systèmes x86 SMP massif utilisant des puces Xeon "Nehalem" EP. L'avantage d'un chipset de commutation QPI serait en effet un relatif agnosticisme vis à vis de l'architecture processeur utilisée. C'est vraisemblablement l'un des axes de recherche de Bull dans le cadre du développement de sa solution d'agrégation de systèmes, car une telle solution aurait aussi des bénéfices dans certains scénarios HPC x86.

L'ensemble des constructeurs concernés (HP, Bull, NEC, Fujitsu et Hitachi) devraient commencer à lever le voile sur leurs plans au cours du dernier trimestre 2008; les premiers serveurs Itanium de nouvelle génération étant attendus au premier semestre 2009. On saura alors jusqu'à quel point les constructeurs de l'écosystème Itanium ont été créatifs…

En savoir plus :