HotChips : AMD présente Zen tandis qu'IBM dévoile son Power9

A l'occasion de la conférence HotChips qui se tenait cette semaine à Santa Clara, AMD et IBM ont levé le voile sur les puces qu'ils entendent mettre sur le ring face aux Xeon d'Intel en 2017.

Depuis le début des années 2010, Intel domine le marché des serveurs sans réelle opposition. Mais l’année 2017 pourrait voir le fondeur affronter une concurrence renouvelée.

AMD veut renaître sur le marché des serveurs

2017 devrait ainsi marquer les premiers vrais pas des serveurs ARM 64 bit, mais c’est surtout de la part d’AMD et d’IBM que la concurrence pourrait être la plus féroce. AMD devrait en effet refaire son entrée sur le marché des serveurs avec une famille de puces connue sous le nom de code « Naples », à base de cœurs « Zen ».

Ce cœur, qu’AMD a dévoilé lors de la conférence HotChips, est annoncé comme 40 % plus performant à fréquence égale que les cœurs « Excavator » motorisant les actuelles puces du fondeur, de quoi repositionner AMD dans la course aux performances sur le marché des serveurs. Les premiers processeurs « Naples » attendus au premier semestre 2017 devraient disposer d’un maximum de 32 cœurs physiques (et 64 threads, Zen implémentant pour la première fois chez AMD, le multithreading). À peu près à la même période IBM devrait lancer ses premières puces Power9, dont les caractéristiques ont été dévoilées en avant-première hier lors de la conférence HotChips.

IBM veut imposer le Power9 comme une alternative aux Xeon d’Intel

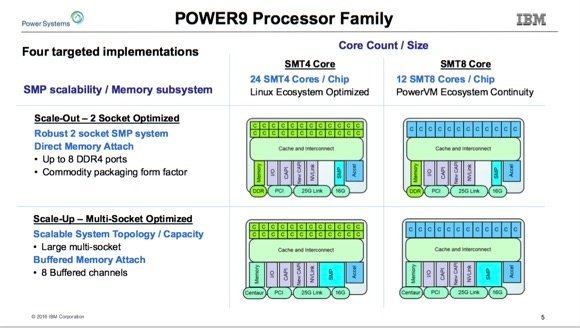

Lors de sa présentation, Brian Thompto, l’un des principaux designers de la puce, a expliqué qu’IBM produirait 4 variantes du Power 9. Il y aura, tout d’abord, en 2017, deux déclinaisons du Power9 SO (pour Scale-out), l’une avec 24 cœurs physiques capables chacun de supporter 4 threads et l’autre avec 12 cœurs à même d’exécuter jusqu’à 8 threads en parrallèle. La première vise principalement le marché des serveurs Linux, tandis que la seconde se destine aux machines Unix traditionnelles.

La future gamme Power9 sera déclinée en 4 versions

La future gamme Power9 sera déclinée en 4 versions

En 2018, IBM proposera deux déclinaisons additionnelles du Power9, les Power9 SU (Scale-Up). Ces puces seront similaires en nombre de cœurs au Power9 SO. Mais elles s’en distingueront par la présence de plus de liens SMP ou par le support du pont mémoire Centaur (qui permet à chaque puce de gérer bien plus de barrettes de RAM). Elles embarqueront aussi des fonctions RAS additionnelles comme Chip Kill (pour se protéger contre la panne d’une puce mémoire sur une barrette DIMM) ou data Lane sparing (pour se protéger contre la défaillance d’une ligne d’accès à la mémoire).

Selon Thompto, les puces Power9 SU auront une bande passante mémoire de 230 Go/s, contre 120 Go/s pour les puces Power9 SO. À titre de comparaison, les Xeon E7 d’Intel ont une bande passante maximale de 102 Go/s tandis que les Xeon E5 v4 plafonnent à 68 Go/s. Les Power9 devraient donc clairement être des monstres de puissance pour ce qui est des opérations de traitement massif de données.

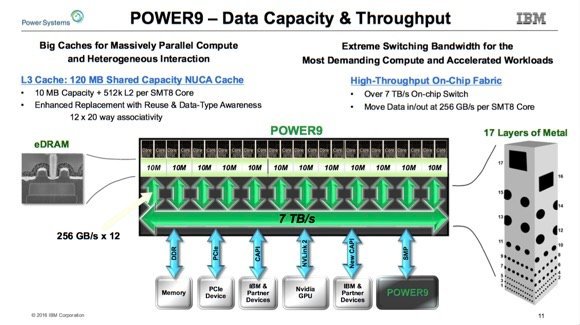

Les puces Power9 seront fabriquées par GlobalFoundries (qui a racheté IBM Microelectronics) en utilisant un processus de gravure en 17 couches à 14 nm. La miniaturisation des transistors et la mise en œuvre de la technologie FinFET devraient permettre de doper considérablement le cache de niveau 3 des processeurs d’IBM, pour le porter à 120 Mo, contre 96 Mo pour le Power8 gravé en 22nm.

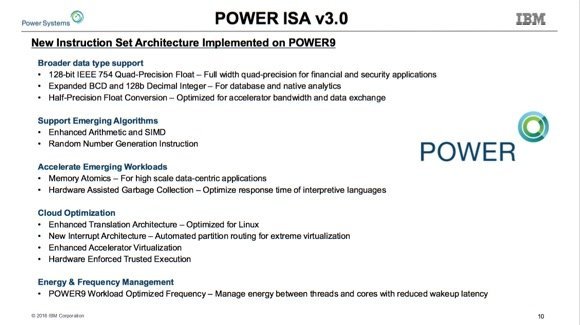

Power9 : un jeu d'instructions modernisé

Power9 : un jeu d'instructions modernisé

Le jeu d’instruction du Power9 a été enrichi. Les puces d’IBM sont désormais capables de réaliser des opérations en virgule flottante à quadruple précision (en 128 bit), et bénéficient de capacités de calcul décimal enrichies. IBM a dopé les fonctions de l’unité SIMD et ajouté des instructions pour la génération de nombres aléatoires. Big Blue a doté la puce de capacités de gestion de la mémoire transactionnelle et a aussi ajouté des fonctions d’accélération matérielle des opérations de garbage collection pour les langages interprétés comme Java, PHP ou Ruby. Des améliorations ont, enfin, été apportées dans la gestion des interruptions et dans la gestion de la translation d’adresses mémoire autant de modifications qui devraient bénéficier aux fonctions de virtualisation.

Une bande passante et des capacités d'entrées/sorties impressionnantes

Une bande passante et des capacités d'entrées/sorties impressionnantes

Selon IBM, la puce est aussi optimisée pour maximiser les entrées sorties. Les Power9 embarquent un switch intégré offrant une bande passante maximale de 7 To/s. Ce switch est interconnecté aux contrôleurs PCIe 4.0 (le Power9 sera sans doute la première puce à supporter la technologie et fournira 48 liens PCIe 4.0), au bus CAPI (qui permet le raccordement direct d’accélérateurs et FPGA tiers), au bus NVLink 2.0 (permettant l’interconnexion à très haut débit de GPU Nvidia Volta) et aux contrôleurs fournissant les liens SMP entre les puces Power9.

Des performances considérablement supérieures à celles du Power8

Des performances considérablement supérieures à celles du Power8

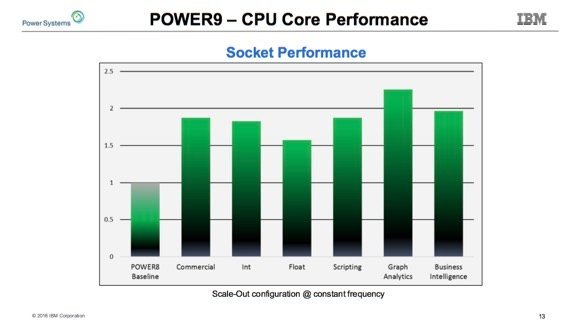

Toutes ces améliorations devraient se traduire par un bond important des performances, comme le montrent les premiers tests comparant le Power8 au Power9, présentés par IBM à HotChips. Les gains vont d’environ 50 % en calcul en virgule flottante à près de 80 % pour les calculs entiers. Des bénéfices similaires devraient être observés sur les applications commerciales. Les applications analytiques afficher des gains de près de 100 à 120 %. Autant dire qu’Intel pourrait avoir du souci à se faire, si IBM et ses partenaires de l’alliance OpenPower arrivent à leurs fins…