Oracle lève le voile sur le Sparc M7

Oracle a profité de la conférence Hot Chips pour lever le voile sur le Sparc M7, son prochain processeur attendu dans des serveurs avant la fin 2015.

Oracle a profité de la 26e conférence HotChips, qui se tenait la semaine dernière à Cupertino, pour lever le voile sur sa future puce Sparc M7. Celle-ci devrait en principe voir le jour vers la mi-2015 et être intégrée dans des serveurs sans doute vers la rentrée de la même année.

Le Sparc M7 devrait être l’unique successeur des actuels Sparc T5 et M6. Gravé en technologie 20nm chez TSMC, il s’appuiera sur une nouvelle génération de cœurs (baptisés S4), plus performants que les actuels cœurs S3 et aussi fonctionnellement bien plus avancés.

Un nouveau coeur doté de fonctions d'accélération applicatives

Le cœur S4 peut traiter 8 threads en parallèle (ou agréger dynamiquement ces threads pour augmenter sa performance monothread), comme le fait actuellement le cœur S3. Il conserve la même profondeur de pipeline que l’actuel S3 mais fonctionnera à une fréquence bien supérieure, du fait notamment de la réduction de la finesse de gravure. Selon Oracle, chaque cœur S3 dispose de son propre contrôleur de consommation (le cœur peut estimer sa consommation électrique avec précision toutes les 250 nanosecondes), ce qui lui permet d’optimiser son fonctionnement mais aussi de respecter les plafonds de consommation qui lui sont imposés. Une des nouveautés par rapport au cœur S3 est l’arrivée de fonctions d’accélération de certains logiciels. Par exemple, les cœurs disposent de la logique nécessaire pour effectuer des contrôles d’intégrité sur les données, accélérer les opérations de « garbage collection » de la Java Virtual Machine, accélérer certaines requêtes de base de données in-memory (et notamment les requêtes portant sur les données en colonnes) et effectuer en matériel des opérations/décompression de données en mémoire.

Des performances annoncées en forte hausse

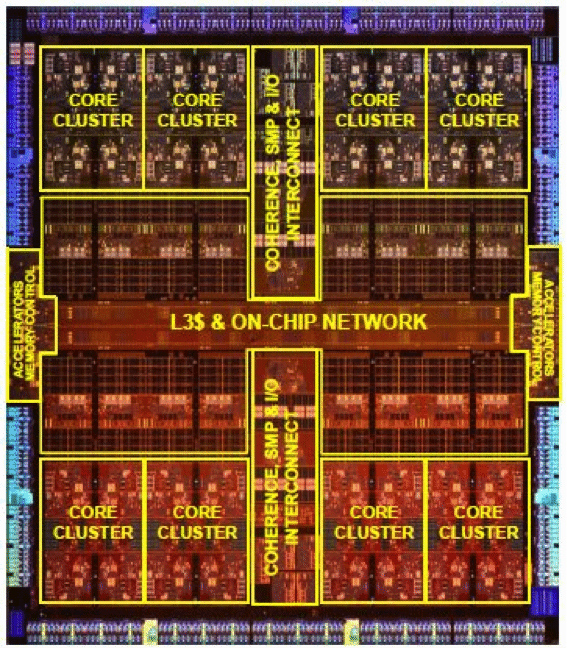

Dans le M7, les cœurs S4 sont groupés par cluster de 4, chaque cluster disposant de 256 Ko de cache d’instruction et de 256 Ko de cache de données partagés entre les cœurs (avec un débit de 500 Go/s). Cette architecture de cluster permet selon Oracle de doubler la bande passante par cœur et de maximiser la performance par thread. Au total, chaque puce M7 dispose de 8 clusters de 4 cœurs, soit un total de 32 cœurs. La puce dispose également de 64 Mo de cache de niveau 3 (découpé en 8x 8Mo) partagé entre les clusters de cœurs avec une bande passante globale de 1,6 To/s, soit cinq fois celles du cache L3 du Sparc M6.

Le M7 dispose également de quatre contrôleurs mémoire DDR4 (capable de gérer 16 barrettes DIMM pour un maximum de 2 To de données par puce) et d’un contrôleur PCI-e Gen3 fournissant 4 liens PCI-e. Chaque puce est enfin équipée de 7 liens de cohérence permettant de la relier à 7 autres puces sans électronique additionnelle et donc de créer des serveurs octo-socket sans avoir à recourir à un contrôleur NUMA spécifique).

Selon Oracle, le M7 devrait être entre 2,6 et 2,8 fois plus performant que l’actuel M6 selon les applications.

Bixby 2 : un nouveau bus d'interconnexion pour des grands serveurs NUMA

En parallèle du développement du Sparc M7, Oracle travaille aussi sur la version 2 de sa puce d’interconnexion Bixby, qui devrait permettre au constructeur de proposer des grands systèmes SPARC à 32 sockets (soit 1024 cœurs ou 8192 threads). Le nouveau Bixby 2 devrait offrir une bande passante quatre fois supérieure à l’actuel et permettre à Oracle de concevoir un grand système aux performances étonnantes. De quoi donner la réplique aux futurs grands systèmes Power8.

Il est à noter que l’interface Bixby2 pourra être utilisée dans un mode non cohérent pour, par exemple, servir d’interface de connexion entre des partitions d’une même machine au sein d’un cluster Oracle RAC à haute performance.