Mémoires non volatiles (1/2) : Pourquoi la Flash continue de dominer le marché

La mémoire Flash a fait son apparition il y a trente ans et elle devrait encore dominer largement l’industrie du fait de la généralisation des technologies 3D NAND. Mais certaines limitations de la Flash ouvrent la voie à l’émergence de technologies alternatives.

La mémoire flash a connu ses premiers succès lorsqu’Intel a livré ses premières puces NOR en 1988. Les puces flash NOR ont, à leur tour, ouvert la voie à la mémoire flash NAND, apparue trois ans plus tard. La NAND a connu l’adoption la plus rapide de toutes les technologies de semi-conducteurs, ses revenus passant de 1,8 milliard de dollars à 18 milliards de dollars en 10 ans à peine. En 2017, la technologie a atteint un chiffre d’affaires record de 50 milliards de dollars, un montant équivalent à l’ensemble des revenus des fabricants de semi-conducteurs en 1990. Clairement, la Flash NAND est devenue l’un des composants clés de l’industrie des semi-conducteurs.

Mais des changements se profilent à l’horizon à mesure que l’industrie met au point de nouvelles techniques de mémoire qui pourraient succéder à la Flash.

La flash NAND touche à ses limites

Au cours des 40 dernières années, le nombre de transistors par puce a doublé tous les ans ou tous les deux ans en réduisant la taille d’un seul bit de 30 % en moyenne par an grâce à la loi de Moore. Cela a entraîné une baisse des coûts qui a permis aux puces de trouver une utilisation plus large. La réduction de la finesse de gravure de 30 % par an (un processus que l’industrie appelle « shrink ») a contribué non seulement à abaisser les coûts de production de la Flash mais aussi à augmenter sa capacité.

Toutefois si la course à la finesse de gravure profite encore aux semi-conducteurs traditionnels comme les processeurs, la mémoire flash touche aux limites de ce qui est possible : dans une mémoire flash, les bits sont stockés sous forme d’électrons sur une grille flottante, et le nombre d’électrons qu’une grille flottante peut contenir est proportionnel à la taille du transistor. À la géométrie de processus de 15 nanomètres (nm), la différence entre un 1 et un 0 n’était que de quelques dizaines d’électrons, un nombre extrêmement difficile à détecter dans le bruit d’une puce numérique. Si les fabricants venaient à réduire encore la taille du transistor de 30 % de plus, comme ils l’ont toujours fait, le nombre d’électrons tomberait sous le niveau détectable. Or en stockage, ne plus faire la différence entre un 0 et un 1 est un problème majeur.

La 3D NAND à la rescousse

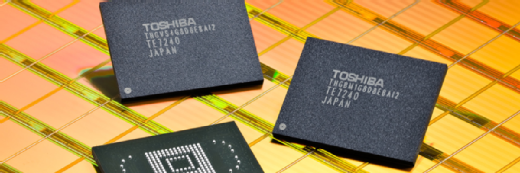

Toshiba a dévoilé une solution intelligente à ce problème en 2006. Plutôt que de continuer à rétrécir les transistors gravés sur la surface d’une puce, pourquoi ne pas créer une structure verticale et construire des transistors le long des murs de la tour, comme les jardins verticaux sur les murs des immeubles de bureaux urbains ?

En utilisant cette approche d’empilage, pour augmenter le nombre de transistors sur une puce, Toshiba a permis de continuer à abaisser le coût d’un bit flash même si les transistors ne pouvaient être mis à l’échelle. Le constructeur a nommé cette approche Bit Cost Scaling, ou BiCS, qui est devenue la base du flash 3D NAND.

Non seulement BiCS permet de poursuivre les réductions de coûts, mais il permet aussi de maintenir la compatibilité avec l’écosystème NAND planaire, les deux technologies étant suffisamment proches pour que leur exploitation par des systèmes informatiques ne nécessite que des modifications à la marge. C’est un avantage essentiel par rapport à d’autres nouvelles technologies de mémoire émergentes.

L’intégralité de l’industrie s’est progressivement convertie à l’approche de Toshiba. Avec BiCS, les bits sont construits dans une colonne formée en remplissant un trou dans une série profonde de couches semi-conductrices. La question qui se pose reste de savoir combien de couches il est possible d’empiler sans toucher aux limites de la technologie ? La réponse est encore loin d’être claire.

Lorsque Toshiba a développé BiCS pour la première fois, la pensée dominante voulait que le nombre de bits dans la colonne soit limité par le nombre de couches dans la puce et la largeur et la profondeur du trou utilisé pour créer la colonne (voir l’encadré). Les fabricants ne peuvent pas faire ce trou plus petit qu’environ 20 nm parce que quelques couches concentriques de matériau doivent recouvrir l’intérieur, et ces couches concentriques ont une épaisseur minimale requise. La profondeur, quant à elle, est proportionnelle au nombre de couches verticales, et ces couches ont également une épaisseur minimale. En raison de ces restrictions, le rapport d’aspect du trou - la profondeur divisée par le diamètre - est déterminé par le nombre de couches verticales dans la flash.

Comprendre la mémoire 3D NAND

La 3D NAND utilise une approche relativement simple pour empiler plus de transistors sur une puce : l’idée est de les construire latéralement, en allant à l’encontre de la façon dont les semi-conducteurs ont toujours été fabriqués.

La plupart des puces sont fabriquées par un procédé photolithographique. Les motifs nécessaires à la fabrication de milliards de transistors sur une puce sont projetés sur la surface d’une tranche de silicium en projetant de la lumière à travers un masque qui ressemble à un négatif photographique, puis en traitant les parties non exposées du silicium. Il s’agit, par nature, d’une approche planaire ; les photographies sont toujours bidimensionnelles.

Alors, comment en faire de la 3D ? Les innovateurs qui ont créé la 3D NAND ont réalisé que certains des motifs hautement répétitifs qu’ils voulaient utiliser pouvaient être construits autrement. S’ils faisaient de nombreuses couches de matériaux à la surface de la puce, quelque chose comme le gâteau et le glaçage d’un gâteau à plusieurs couches, ils pourraient alors graver des trous à travers toutes les couches. Cela produirait une structure qui ressemblerait à une photographie imprimée latéralement sur les parois des trous. Ceci peut être fait sans utiliser de procédé photographique grâce à l’alternance des couches - le motif est déjà dans les couches.

Bien sûr, la technologie est en réalité plus complexe que cela, mais ce concept est le secret de base de la 3D NAND.

Les rapports d’aspect de 40 pour 1 sont difficiles à fabriquer, et 60 pour 1 représente un défi extraordinaire. Mais au fur et à mesure que le nombre de couches augmente, un rapport d’aspect plus élevé est requis. Cela semblait limiter la 3D NAND à trois générations, soit une centaine de couches, avant qu’il ne soit nécessaire de l’abandonner au profit d’une nouvelle technologie.

Mais voilà, les chercheurs dans le domaine des semi-conducteurs sont étonnamment innovants et ils ont mis au point un nouveau concept baptisé empilement de cordes pour supporter un nombre de couches beaucoup plus élevé. Avec l’empilement de cordes, un certain nombre de couches 3D NAND est gravé, puis un autre ensemble de couches est construit au-dessus. À chaque nouvel ensemble de couches, un nouveau trou est formé, mais ce trou est gravé à travers un plus petit nombre de couches, de sorte que son rapport d’aspect reste modeste. Par exemple, au lieu de graver un trou difficile à travers 64 couches, Micron Technology grave deux fois au travers de32 couches pour produire ses puces NAND 3D à 64 couches actuelles. Cela correspond à peu près à la différence entre deux trous avec un rapport d’aspect de 30 pour 1 ou un seul trou avec un rapport d’aspect de 60 pour 1.

Personne ne sait quelles sont les limites à ce mécanisme d’empilement de cordes. L’avis général est que la limite se trouve sans doute aux environs de 500 couches, mais sans certitude absolue. D’autant que par le passé l’avis général a fréquemment été remis en cause dans le monde des semi-conducteurs.

Aujourd’hui, les puces à 64 couches ont des capacités aussi élevées qu’un térabit (128 Go), de sorte qu’une puce à 500 couches pourrait stocker presque 8 fois plus de données. Une puce d’un téraoctet est certainement envisageable. Si une puce d’un téraoctet était construite sur un processus de 500 couches, elle ne serait pas plus grande que son homologue de 64 couches de 128 Go aujourd’hui.

L’impact de l’empilement de cordes est tel que l’on est encore loin d’avoir vu la fin de la Flash 3D NAND. Cela n’empêche pas l’industrie de travailler activement au développement de nouvelles technologies de mémoire alternatives. L’une des premières à faire son apparition sur le marché est la 3D XPoint d’Intel et Micron.

Lire la seconde partie de cet article : Mémoires non volatiles (2/2) : Les successeurs potentiels de la mémoire Flash