Raja Koduri : « le packaging replace Intel en tête des semiconducteurs »

Dans cette interview, le patron du design pour les puces hautement performantes expose une technique d’avant-garde dans l’assemblage des circuits. Elle doit permettre à Intel de produire des puces à l’efficacité inédite.

À la tête de la division Accelerated Computing Systems and Graphics Group (AXG), Raja Koduri est désormais l’ingénieur responsable du design des puces les plus puissantes chez Intel. Historiquement spécialiste des cartes graphiques, sa mission est à présent d’apporter à Intel les GPUs les plus efficaces du marché. LeMagIt a eu l’occasion de l’interroger sur sa stratégie, sur ses secrets de fabrication et même sur ce qu’Intel compte faire en France, où son nouveau centre de R&D pour les puces les plus puissantes doit ouvrir ses portes d’ici à l’année prochaine.

LeMagIT : Pouvez-vous nous expliquer en deux mots votre nouvelle stratégie concernant le développement des semiconducteurs ?

Raja Koduri : Nous travaillons à fournir du supercalcul pour un minimum d’énergie. Le supercalcul n’est plus cantonné aux simulations scientifiques. Aujourd’hui, toutes les entreprises ont besoin d’appliquer de l’intelligence artificielle à une grande variété d’activités qui se font en dehors d’un centre de calcul. C’est ce besoin que nous prenons en considération.

L’exemple extrême est celui des voitures autonomes qui doivent prendre des décisions et qui ne peuvent utiliser qu’une fraction de l’énergie de leur batterie pour alimenter leurs calculs. Si vous regardez l’étendue des traitements que doivent effectuer de tels véhicules très rapidement, vous vous dites que cela reviendrait à mettre un supercalculateur complet sur quatre roues. Mais vous ne pouvez pas mettre un datacenter traditionnel dans une voiture.

Il faut donc améliorer le rendement des puces. La solution pour y parvenir est que la mémoire, qui contient les données, et les cœurs, qui les traitent, fonctionnent à la même vitesse. La différence entre une application standard et des calculs de type HPC est que dans le second cas les jeux de données occupent beaucoup de place. Il ne s’agit plus de faire des designs avec une petite mémoire cache accolée aux cœurs de processeur, mais véritablement d’accoler l’essentiel de la mémoire au processeur, de les rapprocher, de les mettre dans la même puce.

LeMagIT : Vous n’êtes pas les premiers à mettre plusieurs circuits dans une même puce. En quoi vos processeurs sont-ils différents des SoC (System on a Chip) que l’on trouve chez vos concurrents ?

Raja Koduri : Obtenir une bande passante maximale entre une mémoire complète et les cœurs de calcul n’est pas simple à faire. Il faut un packaging spécial, qui supporte de véhiculer des To/s de données. Nos concurrents proposent des Mo/s ou des Go/s.

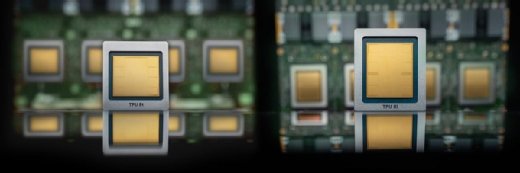

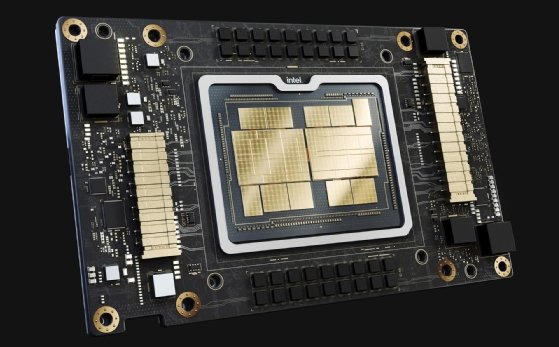

Nous, nous y sommes parvenus. Sur Ponte Vecchio, notre prochain GPU qui illustre la manière dont nous concevrons à présent les puces, nous avons un packaging qui nous permet de faire communiquer tous les circuits entre eux à la vitesse de 8 To/s. C’est un record. Ponte Vecchio atteint une puissance de 1 pétaflops de calcul matriciel et 64 téraflops de calcul vectoriel. C’est-à-dire autant de vitesse dans la paume de votre main que ce que vous trouvez aujourd’hui dans des centres de calcul en cumulant des racks entiers de serveurs.

Intel est le fabricant le plus en avance au monde dans le domaine de l’assemblage de différents circuits dans une puce. Nous remplaçons les connexions classiques par des brins verticaux et horizontaux de quelques dizaines de micromètres de large, si fins qu’il y a très peu de déperditions de vitesse entre les circuits.

Nos concurrents asiatiques, TSMC notamment, nous ont devancés sur la finesse de gravure des circuits. Mais cette technologie d’assemblage va nous permettre de rattraper notre retard et même de repasser en tête dans la course technologique.

LeMagIT : Donc, votre supériorité technologique ne tiendrait finalement qu’à votre meilleur savoir-faire dans l’interconnexion des circuits dans une puce ?

Raja Koduri : Non. Les interconnexions de quelques dizaines de micromètres ne contribuent qu’à 10 ou 20 % de la performance globale. Ce qui multiplie par deux, par quatre, par dix votre efficacité, c’est la combinaison même des circuits que vous assemblez dans la puce et votre capacité à les programmer.

Les transistors dernier cri que proposent nos concurrents ne servent qu’à faire des cœurs de processeur. Mais ils ne sont pas rentables pour fabriquer de la mémoire. Avec notre technique, vous pouvez combiner les circuits les plus efficaces dans chaque génération de transistors et atteindre ainsi les meilleures performances, au meilleur prix, avec les meilleurs délais de livraison sur le marché.

Un point important est que nous investissons beaucoup dans notre capacité à décliner nos produits en différentes configurations. Quand vous savez composer la puce la plus efficace à partir de différents circuits, il suffit de changer tels circuits, de réduire telle quantité de circuits, pour fournir une puce adaptée aux PC, aux voitures, aux équipements embarqués.

LeMagIT : Vous évoquiez aussi un avantage concernant le développement des applications ?

Raja Koduri : Nous mettons aussi au point des outils de développement – la plateforme oneAPI – qui abstraient les calculs scalaires, vectoriels, matriciels. Ainsi, vous n’avez plus besoin de développer votre application pour une configuration précise. Votre application tirera le meilleur parti du matériel sous-jacent.

Si l’on reprend l’exemple de la voiture autonome. Un constructeur ira typiquement entraîner son intelligence artificielle en cloud, sur des serveurs équipés d’une puce avec beaucoup de cœurs matriciels et une mémoire HBM intégrée pour un maximum de performances. En revanche, pour la prise de décision qui se fera dans la voiture, vous n’avez plus besoin d’une bande passante mémoire aussi élevée et d’une telle puissance matricielle. Vous voudrez surtout qu’elle ait suffisamment de cœurs économes en énergie pour prendre des décisions en temps réel, sans impacter l’autonomie de sa batterie. Bien sûr, vous simulerez en amont les réactions de la voiture depuis le cloud.

Avec le même design industriel, nous fournissons les deux configurations de puces et les mêmes outils pour écrire chaque partie du code.

LeMagIT : Concrètement, qu’est-ce que ces puces tout intégrées vont changer au design des serveurs ? Et à la manière de développer des applications ?

Raja Koduri : Cette conception modulaire permet une très grande liberté au niveau de l’architecture des serveurs. Vous pourrez par exemple avoir des serveurs qui seront totalement dépourvus de barrettes mémoire, car vous y aurez déployé des modèles de puces où la mémoire est intégrée, typiquement plus ou moins de GPU Ponte Vecchio avec plus ou moins de Xeon Sapphire Rapids + HBM.

Évidemment, une puce qui intègre la mémoire coûte plus cher qu’une puce qui utilise des barrettes externes. Mais il faut réfléchir à l’échelle de vos serveurs. Si vous avez de gros besoins de calcul haute performance, des puces avec mémoire intégrée vont vous permettre d’avoir des serveurs qui occupent moins de place et consomment moins d’énergie dans votre datacenter, avec un avantage de coût certain.

Nous allons d’ailleurs proposer des séries spéciales de processeurs, adaptées aux designs de serveurs que les grands hébergeurs de cloud développent eux-mêmes pour optimiser leurs datacenters.

À l’inverse, il est certain que des puces avec mémoire HBM intégrée ne vont pas vous apporter beaucoup de bénéfices si vous voulez juste lancer des applications en machines virtuelles. Mais notre capacité industrielle va permettre de proposer simplement d’autres configurations, adaptées à chaque cas d’usage.

En 2024, avec notre projet Falcon Shores, nous franchirons une étape supplémentaire en mixant des cœurs CPU et des cœurs GPU au sein de la même puce. Nous pourrons faire varier les proportions de cœurs et de mémoire embarquée à volonté selon les cas d’usage.

LeMagIT : Ne risquez-vous pas d’augmenter le risque d’une défaillance si vous mettez beaucoup plus de traitements dans une seule puce ?

Raja Koduri : D’abord, avant de commercialiser une puce, nous passons par de nombreuses étapes de validation pour nous assurer qu’un plantage matériel ne puisse pas arriver. Et cette validation est sans doute plus juste à l’échelle d’une puce qu’à l’échelle de tout un rack de serveurs. Mais, surtout, plus vous intégrez, plus vous fiabilisez. Les pannes matérielles arrivent à cause d’effets mécaniques, comme les vibrations, qui impactent les connexions.

C’est d’ailleurs un autre point fort d’Intel : nous ne sommes pas qu’une entreprise d’innovation, nous sommes une entreprise de production. J’aime à dire que le génie, c’est 1 % d’inspiration et 99 % de transpiration. Les 99 % de transpiration sont exactement la question que vous posez : nous réfléchissons pour que nos circuits restent fiables dans différentes conditions, à différents niveaux de température, de chocs, y compris dans une voiture ou dans un drone.

Nous allons même jusqu’à faire en sorte que nos puces ne nécessitent pas des ventilateurs dont la rotation provoquerait des problèmes physiologiques aux équipes techniques. Chez Intel, la conception d’une puce prend ainsi quatre ans et mobilise 3 à 4 000 ingénieurs sur les moindres détails.

LeMagIT : Pour accélérer pleinement une application, ne faudrait-il pas aussi augmenter la vitesse de tout ce qu’il y a autour de la puce ? Le réseau, typiquement ?

Raja Koduri : C’est précisément pour résoudre ces problématiques que nous investissons aujourd’hui dans un centre de R&D en France. L’un de nos projets de recherche, actuellement très important, est tout ce qui a trait à la photonique, c’est-à-dire le fait de relier des connexions en fibre optique directement à des circuits de silicium pour éliminer les déperditions de vitesse également autour des puces. Vous avez à ce titre beaucoup de laboratoires de recherche en Europe dont les travaux sur l’optique nous intéressent au plus haut point.

LeMagIT : Justement, pouvez-vous nous en dire un peu plus sur ce centre de R&D que vous allez installer en France ?

Raja Koduri : L’objectif est, plus généralement, de réfléchir à l’architecture globale. Tout au long de ma carrière, j’ai toujours travaillé à la frontière entre le matériel et le logiciel. C’est là que se trouve le vrai design de l’architecture : parvenir à comprendre, à modéliser comment fonctionne une charge de travail, puis développer un design où tous les aspects matériels sont placés de manière optimale pour cette charge de travail.

Quels traitements pouvons-nous entièrement charger dans une puce ? Comment ? Quels traitements nécessitent de communiquer avec les systèmes autour ? En Europe, vous voulez investir dans de nouvelles ressources d’énergie, dans les réacteurs à fusion nucléaire, vous avez des besoins industriels pour l’IA. Nous pensons que l’Europe a un potentiel énorme pour réfléchir au fonctionnement des applications performantes et trouver comment implémenter les designs correspondants.

Nous allons ouvrir de nombreux postes en France pour la recherche sur les transistors, sur les circuits, sur les systèmes, sur les logiciels et, donc, sur les interconnexions. Nous allons former des jeunes sur tous ces aspects. Ils seront en lien direct avec nos centres de R&D aux USA. Nous étudions actuellement les programmes de formation que nous pourrions mettre en place en nous associant avec des universités locales.

Pour aller plus loin : le détail de Ponte Vecchio

Suite à cette interview, LeMagIT a pu apprendre qu’une puce Ponte Vecchio se compose en effet de circuits – des « tiles » ou « tuiles », dans la nomenclature Intel – issus de différentes chaînes de production. Cela permet à Intel d’aller chercher des ressources qu’il n’a pas, mais aussi de contourner éventuellement une pénurie en changeant de fournisseur.

Les 47 tiles qui composent Ponte Vecchio sont a priori :

- 1 plateau Foveros d’interconnexions verticales et horizontales en 36 micromètres chacune, issu des usines Intel

- 8 modules EMIB d’interconnexions horizontales en 55 micromètres chacune, issus des usines Intel

- 8 circuits de mémoire HBM2e de 16 Go chacun, gravés par Intel en 10 nm

- 16 circuits de calcul composés chacun de 8 cœurs Xe-HPC, gravés par TSMC en 5 nm

- 2 circuits de routage Xe-Link, gravés par TSMC en 7 nm

- 12 circuits de cache L2 de 34 Mo chacun.