Comment AMD entend se relancer sur le marché des serveurs et du HPC

Après avoir indiqué en mai vouloir accélérer à 2016 la sortie de ses prochaines puces Opteron à base de coeur, AMD lève le voile sur ses ambitions dans le HPC.

Après avoir largement été éjecté du marché des serveurs par Intel, AMD travaille officiellement à son retour avec un cœur x86 64 bit de nouvelle génération à même de traiter 40% d’instructions par cycle d’horloge de plus que le cœur Excavator, qui motorise les puces Opteron actuelles.

AMD mise sur le cœur Zen pour se relancer sur le marché des serveurs

Selon le fondeur, les cœurs Zen devraient être les premiers cœurs AMD à supporter le multithreading symétrique ou SMT, à l’instar des puces Xeon et Core d’Intel, des puces Sparc d’Oracle ou des puces Power d’IBM. Ils bénéficieront aussi des dernières avancées en matière de gravure, puisqu’ils devraient être gravés en 14nm. Ceci mettra AMD sur un pied d’égalité avec Intel en matière de fabrication, une première depuis plus de dix ans. Si tout se passe comme prévu, on devrait voir des puces Opteron disposant d’au moins 16 cœurs capables de traiter 32 threads en parallèle et peut-être plus.

Des puces serveurs avec une mémoire rapide intégrée

AMD indique que ses prochaines puces serveurs disposeront d’une bande passante mémoire hors du commun, ce qui implique que le fondeur appliquera à ses prochains Opteron les technologies de mémoire HBM développées pour ses cartes graphiques (le processeur embarquera directement un ensemble de puces mémoires empilées les unes sur les autres, vraisemblablement 8 à 16 Go de mémoire).

AMD devrait aussi rattraper son retard en matière d’entrées/sorties en embarquant en standard dans ses puces les capacités nécessaires pour supporter des interfaces réseaux rapides. En fait selon la firme, les puces à architectures Zen devraient lui permettre d’être à nouveau compétitif sur le marché des serveurs. Une affirmation qui, si elle se vérifie, pourrait signifier un retour à des prix plus sages sur le marché des puces serveurs, Intel ayant profité de la faiblesse de son concurrent pour remonter les prix de ses puces.

Des puces hybrides CPU/GPU conçues spécifiquement pour le marché HPC

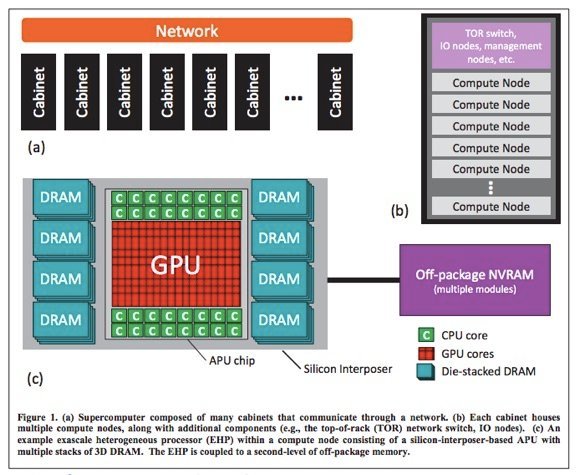

Mais la stratégie serveur d’AMD va au delà des puces serveurs pour le marché des entreprises. Dans un article publié dans la revue Micro de l’IEEE, plusieurs responsables R&D d’AMD font le point sur les travaux de la firme en matière de développement d’une architecture serveur permettant d’atteindre l’exaflops.

L'architecture HPC Exascale d'AMD

L'architecture HPC Exascale d'AMD

Le but d’AMD est de créer un APU serveur (une combinaison entre un GPU et un CPU) embarquant 32 cœurs Zen couplés à un GPU de nouvelle génération (probablement un GPU de la génération Greenland) ainsi qu’une grande quantité de mémoire HBM. Du fait de l’intégration de cette mémoire, ce monstre de performance, qu’AMD appelle un EHP (Exascale Heterogeneous Processor), devrait offrir une bande passante mémoire très élevée.

En fait ,AMD pourra s’appuyer sur la mémoire HBM pour offrir des performances optimales à certains codes ou pour servir de cache à très haut débit aux vastes quantités de mémoire DDR4 externe gérées par les multiples canaux DDR4 fournis par le contrôleur mémoire intégré à la puce. AMD évoque même la possibilité d’intégrer des modules de mémoire non volatile (comme de la Flash NAND, des mémoires à changement de phase ou des Memristor) à cette hiérarchie mémoire pour doper encore plus la capacité de chaque noeud.

La gestion de cette hiérarchie mémoire et des affinités entre cœurs, applications et mémoire devrait sans doute faire l’objet d’optimisations intéressantes par les hyperviseurs et OS.

Supporter à la fois les applications parallèles et les codes classiques

Il est à noter que l’architecture hybride de la puce devrait permettre de supporter à la fois des codes parallèles optimisés pour l’architecture massivement parallèle de la partie GPU de la puce et les applications non parallèlisables ou non encore optimisées, une capacité importante pour les grands clients du monde HPC.

AMD mise aussi sur le support de son architecture HSA qui permettra à l’EHP d’affecter au mieux les différentes tâches aux différents composants de l’EHP (GPU, CPU, Accélérateurs spécifiques) en fonction de leur degré de parallèlisation.

Selon l’article d’AMD, les EHP devraient faire leur apparition en 2016/2017, ce qui veut sans doute dire entre la fin 2016 et le début 2017, c’est à dire après le lancement des nouveaux Opteron à base de cœurs Zen, attendus eux en 2016