HSA 1.0 pose les fondations pour le parallélisme hétérogène

La version 1.0 de la spécification,pilotée par AMD, ARM, Qualcomm, Samsung, etc... définit un standard unifié pour la conception et l'exécution d'applications parallèles sur des processeurs hétérogènes.

La fondation HSA, qui réunit entre autres AMD, ARM, BroadCom, Huawei, Imagination Technologies, LG, Mediatek, Oracle, Qualcomm, Samsung, Texas Instruments ainsi que de multiples organismes de recherche a officiellement publié la version 1.0 de sa spécification « Heterogeneous System Architecture », dont l’ambition est de permettre à des développeurs d’exploiter simplement les capacités parallèles des puces hybrides modernes (CPU/GPU) et ce quelle que soit la plate-forme processeur sous-jacente. Une ambition secondaire est de permettre la réduction de la consommation énergétique des puces modernes en faisant en sorte que chaque tâche soit traitée par le composant du processeur le mieux adapté pour ce faire (réduire les cycles CPU consommés, permet aussi de réduire la consommation…)

HSA : Une architecture unifiée pour l'exécution de codes parallèles sur des architectures processeurs hétérogènes

La spécification HSA définit un modèle matériel ou les GPU et autres processeurs de traitement de signal rattachés aux cœurs CPU peuvent avoir un accès transparent et cohérent à la mémoire vive du système, ce qui permet à ces « processeurs » parallèles de partager les informations mises en mémoire par le processeur central (CPU). Dans ce modèle, un CPU et un GPU peuvent travailler en parallèle sur les mêmes données afin d’accélérer des codes parallèlisables (notamment dans les applications HPC) mais aussi des applications plus « banales » comme la reconnaissance vocale, le transcodage de média ou la reconnaissance vidéo.

Mais elle ne se contente pas de spécifier le fonctionnement de certains éléments du processeur. La spécification garantit aussi la portabilité des applications conforme à HSA et ce quelle que soit la plate-forme sur laquelle elles doivent s’exécuter. Pour être clair, une application qui se conforme au modèle de programmation HSA pourra fonctionner indifféremment sur une puce x86 d’AMD sur une puce mobile ARM de Qualcomm ou sur une puce serveur d’Oracle, pour peu que ces puces se conforment à la spécification et fournissent les outils de compilation qu’elle requiert.

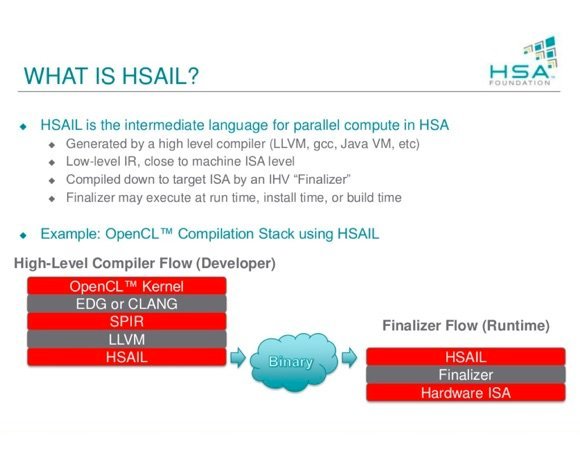

Le principe est assez simple. La spécification HSA définit une ISA (Instruction Set Architecture) virtuelle commune à tous les fabricants et destinée à l’optimisation des codes parallèles sur l’ensemble des plates-formes supportés. Baptisée HSAIL, cette ISA se présente sous la forme d’un langage intermédiaire qui peut être généré par un compilateur de haut niveau (tel que LLVM, gcc, une Java VM, etc.). Le modèle s’accommode donc de multiples langages tels que Java, C++ (notons qu’OpenCL et C++ AMP sont aussi supportés), Python, Fortran et modèles de programmation comme OpenMP. Selon la fondation HSA, le modèle mémoire défini par HSA est aussi compatible avec celui de Java et de .Net, deux points essentiels dans l’adoption de la technologie par les développeurs d’OS. Java est d’ailleurs une cible de choix puisque via la technologie Aparapi, la fondation HSA estime possible de doper de façon significative la performance des codes parallèles Java sans avoir à les modifier. Des travaux sont aussi menés conjointement entre AMD et Oracle pour assurer que Java 9 tirera pleinement parti des capacités des puces HSA (via le projet Sumatra).

HSAIL : vers une compilation des applications en deux temps

Dans la pratique HSAIL nécessite la mise en œuvre d’un modèle de compilation à deux étapes. À partir d’un code source, un compilateur de premier niveau (par exemple LLVM) génère un code intermédiaire HSAIL. Ce code doit ensuite être compilé vers la plate-forme cible par un « Finalizer » qui génère un code spécifiquement optimisé à l’ISA cible à partir du code intermédiaire. Cette étape de « compilation », qu’AMD décrit comme s’effectuant en quasi temps réel, peut intervenir lors de la réalisation du logiciel par l’éditeur (auquel cas, l’éditeur devra fournir autant de binaires que de plates-formes cibles). Elle peut aussi se faire lors de l’installation du logiciel ou lors du runtime. Dans ce dernier cas, le système d’exploitation cible devra disposer de la couche de runtime adaptée (le noyau Linux 3.19 a posé les bases du support de HSA).

Le principe de la compilation en deux étapes avec HSAIL

Le principe de la compilation en deux étapes avec HSAIL

La promesse de la fondation HSA est de simplifier la parallélisation des codes à l’échelle d’un grand nombre de plates-formes matérielles et ce sans que les développeurs n’aient à apporter d’optimisations spécifiques pour chaque plate-forme. Un autre objectif, au travers du modèle de partage de mémoire défini par la spécification, est d’élargir le spectre d’utilisation des GPU et coprocesseurs dans les processeurs modernes afin de contribuer à l’accélération des codes parallèlisables modernes.

À ce jour, les puces Kaveri d’AMD sont compatibles avec une version préliminaire de la spécification HSA et servent de plates-formes de développement. Les puces Carrizo, basées sur le nouveau cœur x86 « Excavator » de la firme, qui sont dans le courant du premier semestre 2015, seront, quant à elles, les premières à supporter la totalité de la spécification dans sa version 1.0. Ce sera alors au tour des différents fondeurs de puces ARM de la fondation de fourbir leurs propres armes pour se lancer dans la bataille.

Clairement, Intel et Nvidia, qui se sont tenus à l'écart de la fondation HSA, sont dans la ligne de mire des membres de la fondation. AMD entend notamment faire de la spécification un tremplin pour se relancer dans le monde du HPC face à Nvidia et Intel, mais aussi pour s’assurer que les développeurs tirent pleinement parti des capacités parallèles de ses puces. Les fabricants ARM y voient, de leur côté, un moyen d’accélérer leur percée dans le monde des serveurs, mais aussi une façon de fournir un modèle standard pour le déploiement d’applications nécessitant des codes parallèles (reconnaissance faciale, reconnaissance de forme…) sur les terminaux mobiles et les terminaux embarqués (on pense par exemple à l'automobile)…