Rainer - Fotolia

En reprenant les travaux d'Applied Micro, Ampere veut s'imposer sur le marché des serveurs ARM

Né du rachat des activités processeur serveur ARM de l'ex-Applied Micro par le fonds Carlyle Group, Ampere Computing veut s'imposer sur le marché des processeurs pour serveurs ARM. Son processeur Ampere, fruit des travaux d'Applied Micro sur le X-Gene3 devra affronter les Centriq 2400 de Qualcomm et les ThunderX2 de Cavium.

Après pris le contrôle l’an passé de l’activité processeurs ARM de Macom (ex-Applied Micro), le fonds d’investissement Carlyle Group vient de rebaptiser l’entreprise Ampere Computing et de nommer Renée James, l’ex-présidente d’Intel à sa tête. Carlyle a racheté l’activité pour un montant non précisé, mais Macom a indiqué que ses 20 % du capital qu’il conserve dans la firme sont valorisés 36,5 M$.

Ampere a hérité de l’ensemble du savoir-faire d’Applied Micro en matière de processeurs serveur ARM 64 bit – l’ex-gamme X-Gene, désormais Ampere CPU — et a également repris les quelque 300 salariés de la société. Ampere a son siège à Santa Clara dans les anciens locaux d’Applied Micro, à deux pas d’Intel. La firme dispose aussi de bureaux à Portland au Vietnam et en Inde.

Applied Micro, un pionnier des puces serveurs ARM

Applied Micro a pris une licence d’architecture ARM en 2010 et a pour la première fois dévoilé ses plans de développement d’une famille de processeurs serveur ARM en 2011. à la fin 2013, la société a démontré le premier prototype fonctionnel du X-Gene, une puce gravée en 40 nm et disposant de 8 cœurs à 2,4 GHz et d’un support intégré pour deux ports 10G Ethernet. Les premiers serveurs équipés du SOC X-Gene (nom de code « Storm ») sont apparus en 2014 chez HPE sous forme de « cartouches » pour les serveurs Proliant MoonShot. Mais ces machines n’ont connu qu’un succès d’estime.

Applied Micro s’est rapidement remis au travail et a dévoilé une roadmap comprenant deux nouvelles familles de puces, le X-Gene 2 et le X-Gene 3. Le premier (nom de code « Shadowcat ») est apparu à la fin 2015. Gravée en 28 nm, il embarque entre 8 et 16 cœurs cadencés entre 2,4 et 2,8 GHz. Il a notamment été utilisé dans le cadre de prototypes HPC, mais aussi dans des systèmes embarqués. HPE, par exemple, a utilisé des puces X-Gene 2 pour ses baies de stockage StoreVirtual 3200.

Ampere mise sur le design du X-Gene 3

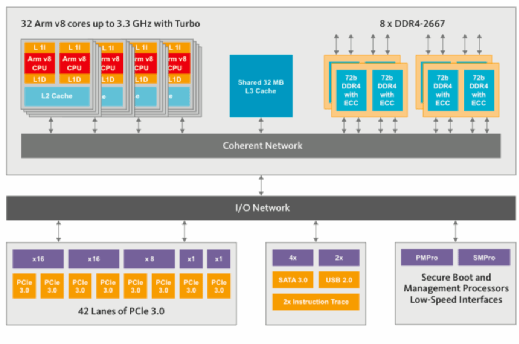

En 2016, Applied Micro a levé le voile sur le X-Gene 3 (nom de code « Skylark »), une puce massivement multicœur. Gravée en technologie FinFET à 16 nm, la puce embarque 32 cœurs cadencés à 3 GHz (3,3 GHz en mode Turbo) et dispose d’un total de 4 Mo de cache de niveau 2 (256 Ko par paire de cœurs) et de 32 Mo de cache de niveau 3. Côté mémoire, elle intègre un contrôleur gérant 8 canaux mémoires pour DIMM DDR-4 et capable de piloter jusqu’à 1 To de RAM par socket. La partie I/O offre 42 lignes PCIe Gen 3, 4 ports SATA ainsi que 2 ports USB 2.0.

Il est à noter qu’à l’origine, Applied Micro a conçu la puce aussi bien pour des usages scale-out que pour des usages scale-up, en prévoyant notamment la possibilité d’interconnecter plusieurs processeurs X-Gene 3 entre eux au sein d’un même système. Cette aptitude au scale-up n’est toutefois pas documentée dans la seule fiche produit aujourd’hui disponible sur le site d’Ampere.

Retardé à de multiples reprises par les divers rachats qu’a connus l’activité processeur d’Applied Micro, le lancement officiel du X-Gene 3 ne devrait plus tarder sous son nouveau nom d’Ampere CPU. Le processeur devra non seulement affronter les Xeon d’Intel et les puces EPYC d’AMD, mais aussi plusieurs concurrents sur le marché des puces ARM 64 bit, dont les Centriq 2400 de Qualcomm et les puces ThunderX2 de Cavium (utilisées par exemple par HPE, Bull ou Cray dans des systèmes HPC ou par Microsoft dans son cloud Azure). Pour mémoire, Cavium fait actuellement l’objet d’une offre de rachat de Marvell.