Hoda Bogdan - stock.adobe.com

Serveurs : le bus PCIe 8.0 se dévoile

La version des bus PCIe en cours de standardisation doit rendre possibles des vitesses de transfert huit fois supérieures à celles de l’actuel bus PCIe 5.0. Mais il est peu probable qu’elle arrive en 2028, ce qui était initialement prévu.

Jusqu’à 1 To/s de bande passante entre un processeur et une carte GPU et, ce, dans un serveur rack conventionnel ou un PC de bureau. Telle est la promesse du futur bus PCIe 8.0 dont une version 0.5 du standard vient d’être communiquée aux fabricants informatiques. L’objectif du consortium PCI-SIG responsable de cette norme est que les processeurs, les cartes mères, les cartes accélératrices (IA, réseau…) et les SSD NVMe soient tous compatibles d’ici à fin 2028. Ce qui ne sera vraisemblablement pas le cas.

La caractéristique la plus saillante de ce standard est que chacune de ses voies de communication transportera 256 Gbit/s, soit huit fois plus que celles des bus PCIe 5.0 qui équipent de nos jours les serveurs dernier cri. Il faut diviser par 8 cette valeur pour obtenir un chiffre en Go/s, soit 32 Go/s par voie de communication.

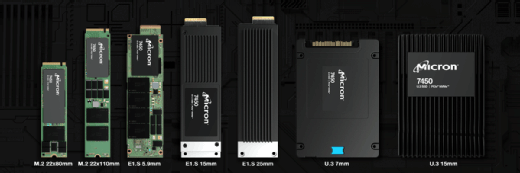

Une carte accélératrice communique avec sa machine hôte sur un maximum de 16 voies, d’où le téraoctet par seconde annoncé. Un SSD NVMe de type datacenter utilise classiquement quatre voies (contre deux sur des SSD pour PC) et offrirait pour sa part une bande passante maximale de 256 Go/s. Toutefois, la latence des circuits NAND qui composent un tel disque Flash ne permet jamais d’atteindre le plafond maximal.

Un autre point technique intéressant est le protocole PAM4 qui offre la possibilité de transférer un bit utile pour chaque bit communiqué, permettant ainsi que les gigatransferts par seconde (GT/s) exprimés par les constructeurs d’équipements PCIe correspondent réellement à des Gbit/s. Ce protocole est implémenté dès la génération PCIe 6.0 qui devrait arriver avec les nouvelles générations de processeurs Xeon et Epyc.

Sur l’actuelle génération PCI 5.0 et depuis la génération PCIe 3.0, le protocole NRZ utilisé demande de communiquer 130 bits pour obtenir 128 bits de données utiles. En PCIe 1.0 et 2.0, il fallait communiquer 10 bits pour obtenir 8 bits de données utiles.

Le bus PCIe 7.0 est quant à lui censé arriver dans les équipements informatiques en 2027. Toutefois, ces calendriers paraissent tous trop serrés, au regard des rythmes d’évolution actuels des processeurs et des circuits de NAND.

Le marché ne suivra pas une évolution aussi rapide

Normalement, le bus PCIe 6.0 aurait dû se généraliser cette année. Cependant, les Xeon 7 Diamond Rapids d’Intel et les Epyc 9006 Venice d’AMD qui supportent ce bus ne seront pas disponibles dans les serveurs avant le début de l’année prochaine.

Leur retard est autant dû à des raisons techniques, qu’économiques ou politiques. Elles sont liées à des changements de stratégie concernant les usines de semiconducteurs, à un contexte où la demande a inhabituellement explosé pour des puces davantage spécialisées en IA, et à des questions géopolitiques qui imposent de déménager les chaînes de production de l’Asie vers les USA. Il est donc probable que l’arrivée des bus PCIe 7.0 puis 8.0 glissent d’autant.

Techniquement, il n’y aura en théorie pas de problème pour que les cartes accélératrices tirent pleinement parti des vitesses offertes par les nouvelles générations de bus PCIe, puisque les puces de ces cartes communiquent déjà bien plus rapidement avec leur mémoire embarquée.

En revanche, les fabricants de SSD NVMe devront certainement s’efforcer de moderniser drastiquement leurs composants électroniques pour suivre l’évolution des performances. À titre d’exemple, Micron a commercialisé en fin d’année dernière un SSD 9650 TLC déjà compatible avec un bus PCIe 6.0, mais dont les débits plafonneront à 28 Go/s en lecture et 14 Go/s en écriture ; alors que ce bus permet en théorie d’atteindre 64 Go/s sur quatre voies.

Dans ce cas, la latence des circuits NAND n’est pas seule en cause. Le SSD n’intègre pas non plus suffisamment de circuits NAND en parallèle pour occuper toute la bande passante du bus. Il y a d’abord une question de place disponible dans le boîtier du SSD. Les circuits NAND TLC conçus par Micron, ici de génération G9, sont individuellement capables d’atteindre 3,6 Go/s. Il faudrait donc en mettre 18. Le problème vient aussi du contrôleur intégré au SSD, qui n’est pas encore capable de router autant de bande passante vers autant de circuits NAND.

La solution que retiennent les constructeurs est généralement de compenser la faible vitesse des circuits NAND par l’ajout de circuits DRAM, bien plus denses et rapides, pour faire office de cache. Problème, cette approche augmente de manière exponentielle le coût du SSD. Faute de technique adéquate, la vitesse des SSD NVMe est donc actuellement limitée par des questions économiques.