Intel lance le Xeon E7 v3, un processeur taillé pour le « In-Memory »

Rolls du processeur X86 dans la gamme d’Intel, le Xeon E7v3 est le plus puissant des Xeon, mais aussi le plus cher. Une puissance qui le destine au monde du HPC, mais pas uniquement. L’analytique « In-Memory », notamment SAP HANA profite pleinement de ses capacités d’adressage mémoire record.

Trônant tout en haut de la gamme des microprocesseurs Inter Xeon, le E7 bénéficie d’une nouvelle mise à jour majeure avec l’architecture Haswell. La version 3 de cette imposante puce (le die mesure à lui seul 3 cm sur 2cm), gravée en 22nm, compte 5,7 milliards de transistors.

Elle marque l’arrivée de versions 18 cœurs tandis que le cache de niveau 3 passe de 37,5 Mo à 45 Mo, le support de la mémoire DDR4 à 1600 MHZ et 1866 MHz. La bande passante du QPI (Intel Quickpath Interconnect), l’architecture Numa d’Intel augmente aussi significativement. Les 3 bus de communication rapides entre puces Xeon d’un même système passent de 3x 8 GT/s (gigatransferts par seconde) à 3 x 9,6 GT/s.

Une évolution d’architecture intéressante pour les applications massivement multi-thread

20% de cœurs en plus, 20% de mémoire cache en plus, les apports de cette nouvelle génération sont relativement classiques chez Intel. Néanmoins, ce Xeon E7 v3 présente néanmoins quelques évolutions intéressantes qui pourraient avoir de grosses conséquences au niveau des applicatifs.

Intel mise ainsi beaucoup sur le jeu d’instruction TSX (Transactional Synchronization Extensions) apporté au Xeon E7 par Haswell pour conquérir le marché des grandes bases de données. Ce jeu d’instruction, utilisé de manière explicite par l’application ou de manière automatique par le microprocesseur, résout pour partie le problème du blocage des zones mémoires utilisées par les threads lors de leur exécution.

Les instructions TSX vont permettre au processeur d’analyser si, au moment où les traitements d’un thread sont bloqués, il existe une dépendance entre ce thread et sa zone de mémoire bloquée et un autre thread en attente en file d’attente. Si aucune donnée n’est susceptible d’être utilisée par un autre thread, celui-ci est immédiatement exécuté, de manière opportuniste, sans attendre que le premier se débloque.

De cette manière, beaucoup moins de threads restent bloqués en attente de traitement dans le processeur. « En moyenne, sur des codes HPC, le gain de performance peut atteindre de 40 à 42%, car on bloque beaucoup moins la mémoire et les threads peuvent être lancés plus rapidement » argumente Stanislas Odinot, évangéliste avant-vente chez Intel qui ajoute : « c’est une fonctionnalité qui nous a été demandée par des gens qui font beaucoup de base de données, des applications qui sont massivement multi-threads, massivement vectorielles et adressent des quantités de mémoire colossales. Bloquer des zones mémoire pénalisait les performances de leurs bases de données. »

La fonction TSX, buggée sur les E5 v3 sortis plus tôt, a été désactivée via un patch, mais les E7 v3 en disposeront bien, assure Stanislas Odinot. Si Intel parvient à fiabiliser cette fonctionnalité, les gains pourraient être substantiels.

Autre chantier entrepris par Intel sur ses Xeon haut de gamme, la fiabilité des systèmes. Héritées de l’Itanium, les fonctions Intel « Run Sure » ont été introduites sur les E7 v2 et continuent d’évoluer.

Il s’agit de garantir au mieux la fiabilité des données stockées dans ces très grandes plages mémoire. Un Xeon E7 v3 peut désormais gérer jusqu’à 24 bancs mémoire.

« Nous avons voulu gérer l’intégrité des données à tous les niveaux, que ce soit au niveau de la barrette DDR4, dans le buffer et dans le micro-processeur, dans la communication inter-CPU et dans la communication PCIe » ajoute l’évangéliste, « C’est un différenciant fort de la gamme E7 par rapport à toutes nos autres gammes processeur. »

Par exemple, il est maintenant possible pour une application de réaliser un mirroring de plage mémoire sur un autre système et avoir une haute disponibilité de zones mémoires très fines, un mirroring qui n’était jusqu’à présent possible que de barrette à barrette.

S’appuyant sur les études d’ITIC (Information Technology Intelligence Consulting), Intel considère que désormais la plateforme Xeon E7 sous Linux et sous Windows a rattrapé son retard en termes de taux de disponibilité sur les meilleurs systèmes RISC.

Quelles applications pour un processeur aussi coûteux ?

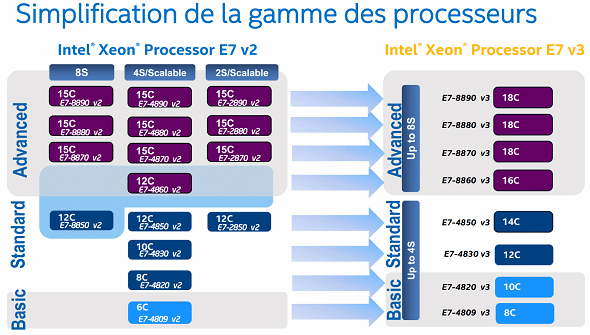

Une fois n’est pas coutume, Intel profite de cette nouvelle génération de Xeon E7 pour simplifier son catalogue.

Ce Xeon E7 v3 est disponibles en 4 versions basiques et standards allant jusqu’à 4 sockets et un nombre de cœurs de 8, 10, 12 ou 14. Les versions les plus puissantes peuvent monter jusqu’à 8 sockets et de 16 à 18 cœurs par processeur.

Une configuration poids lourd qui peut ainsi compter jusqu’à 144 cœurs et adresser la bagatelle de 12 To de RAM DDR4 dans un même système. Une bête de course mais que peu d’entreprises pourront s’offrir puisque rien que pour la mémoire, la facture peut rapidement monter à plusieurs centaines de milliers de dollars pour des systèmes de plusieurs To de RAM.

Le Xeon E7 v3 est proposé de 1224 $ (par quantité de 1 000) à plus de 7 175 $ pièce pour sa version la plus puissante.

Un coût très élevé qui destine cette puce au marché HPC où les clients seront prêt à payer cher pour bénéficier des 50% d’efficacité énergétique additionnels apportés par cet E7 v3, mais qui lui barre l’accès du marché Cloud.

Les fournisseurs, engagés dans une intense bataille des prix, préféreront l’équation coût/performance du Xeon E5. Même sur le marché de la virtualisation, Intel peine à imposer son E7.

Seul le secteur financier ou quelques acteurs du Web ont les poches suffisamment profondes pour s’offrir de tels systèmes x86.

Pour Stanislas Odinot, la cible du Xeon E7 est clairement aujourd’hui les plateformes analytiques temps réel. Oracle avait fait le choix du Xeon E7 V1 puis V2 pour motoriser ses appliances Exalytics, demandant même à Intel de lui produire des versions optimisées pour cet usage. Cela devrait être encore le cas pour la V3 que l’on va prochainement retrouver chez les appliances du rival SAP.

Intel a beaucoup travaillé avec l’éditeur pour que HANA profite à plein des avancées apportées par Haswell. L’américain évoque une multiplication par 6 du nombre d’instance supportée par une appliance HANA lors des tests de qualifications de la puce réalisés avec SAP. Un chiffre à prendre avec des pincettes, mais qui traduit bien les espoirs placés par Intel sur ce marché des appliances « In-Memory ».

Des appliances qui pourront bénéficier de l’E7 v3 dans une approche « scale up » avec une montée en puissance des machines. Une approche qui n’empêche pas Intel de positionner son processeur dans le monde Hadoop où l’approche est plutôt « scale-out », avec la multiplication de plateformes de moindre puissance.

Intel, qui a investi 740 millions de dollars dans Cloudera, estime que son Xeon E7 v3 pourra faire ses preuves notamment sur la solution « In-Memory » Open Source Apache Spark. Une solution qui fait bien évidemment partie de la distribution Cloudera Enterprise. Les puces Xeon E7 v3 seront disponibles dans les 45 jours.